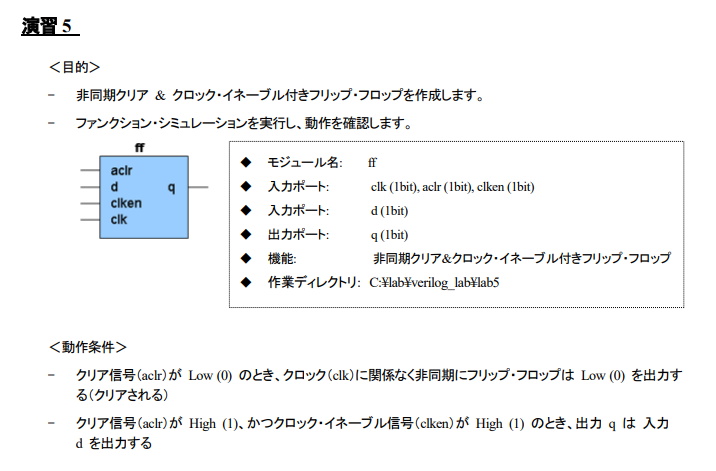

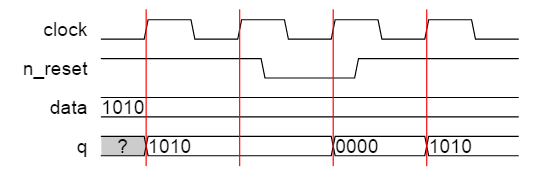

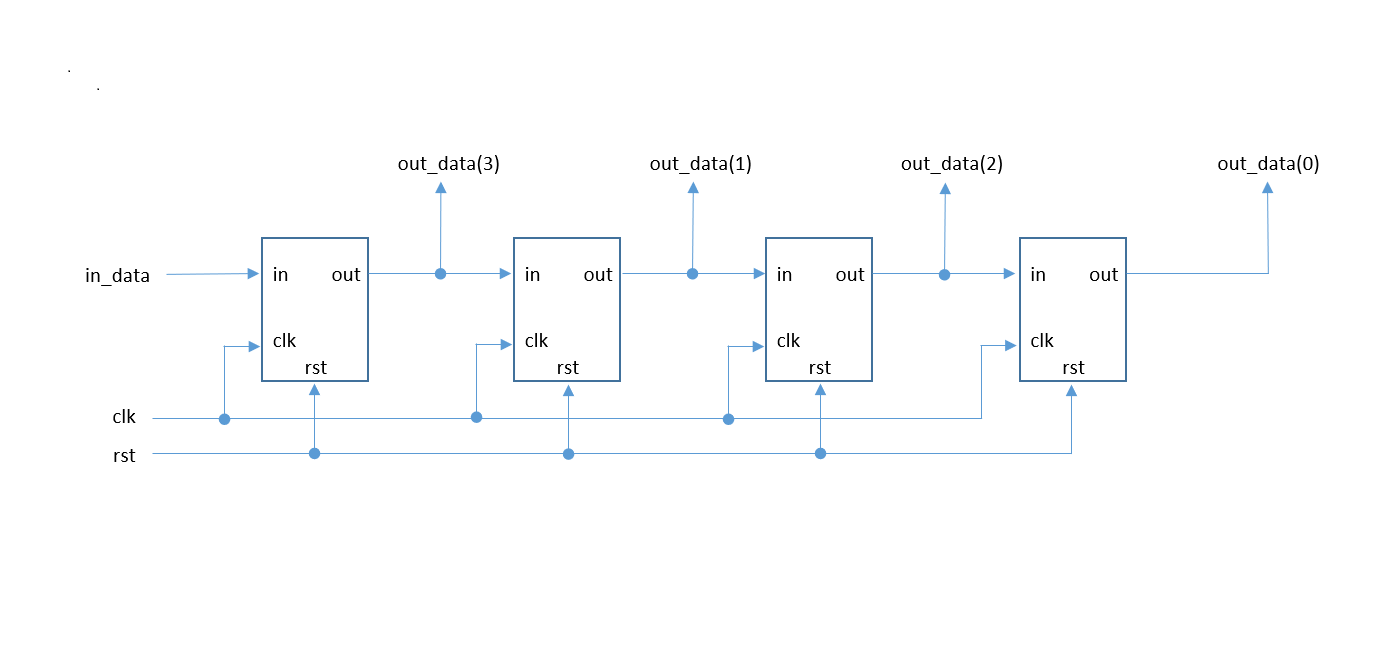

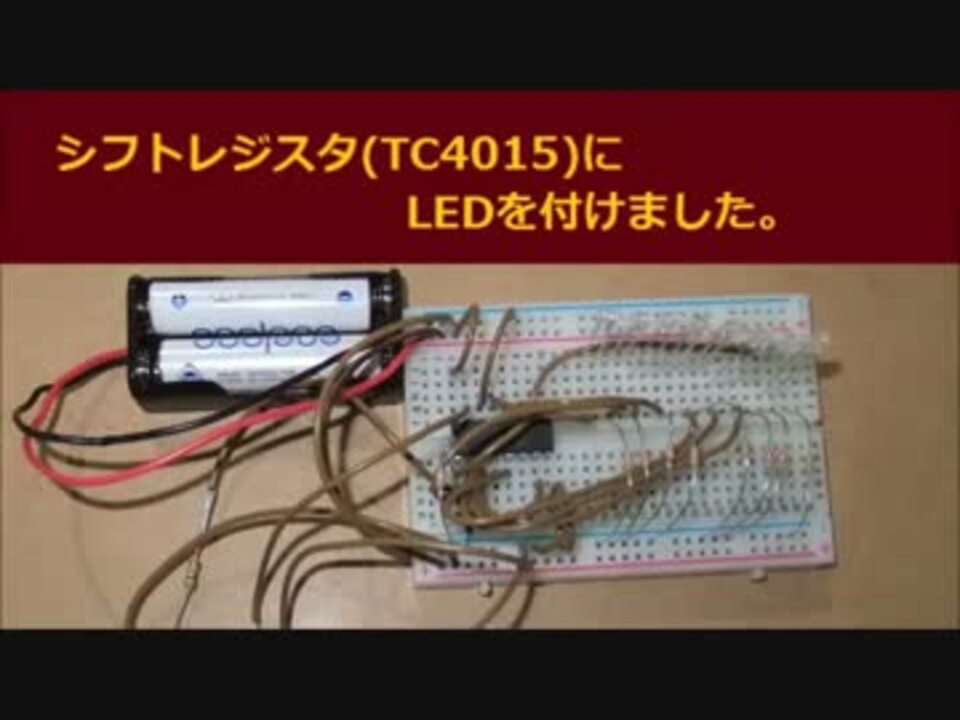

次のVerilogシフトレジスタコードのヘルプを探しますか?次のコードが私に与えられました。私の仕事はそれを回路図形式に変換することです。 module shift_register( output reg 90 out_q, input clk, input reset, input test, input in_cg, input

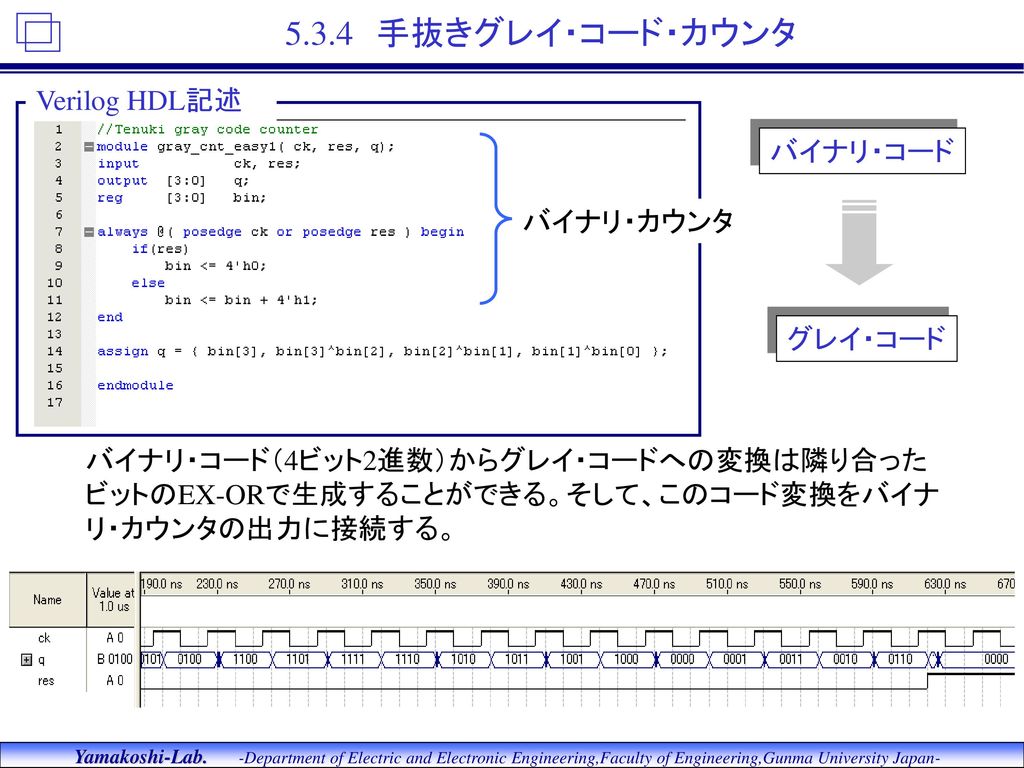

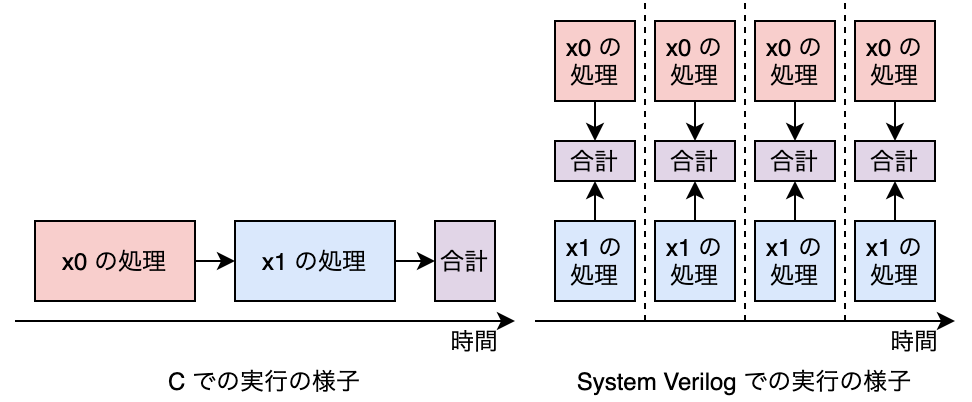

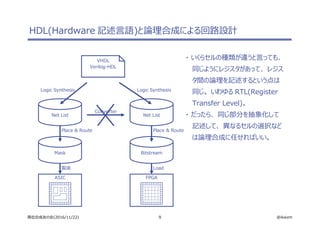

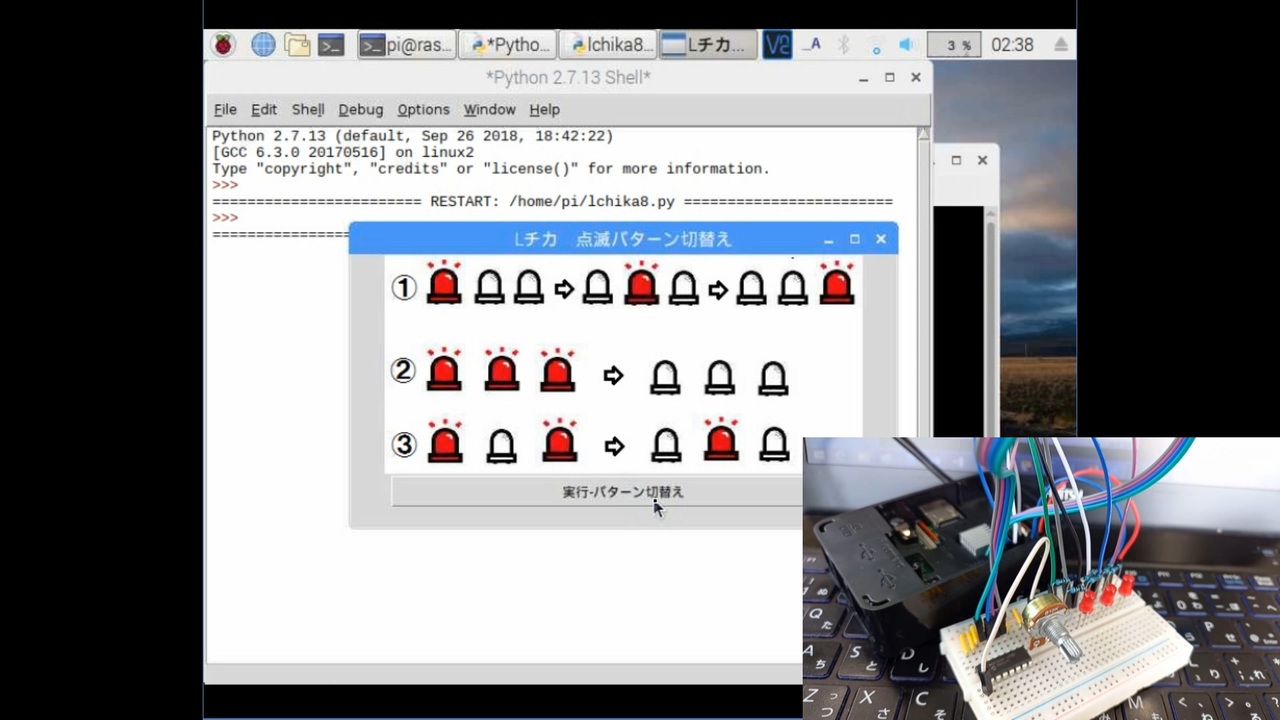

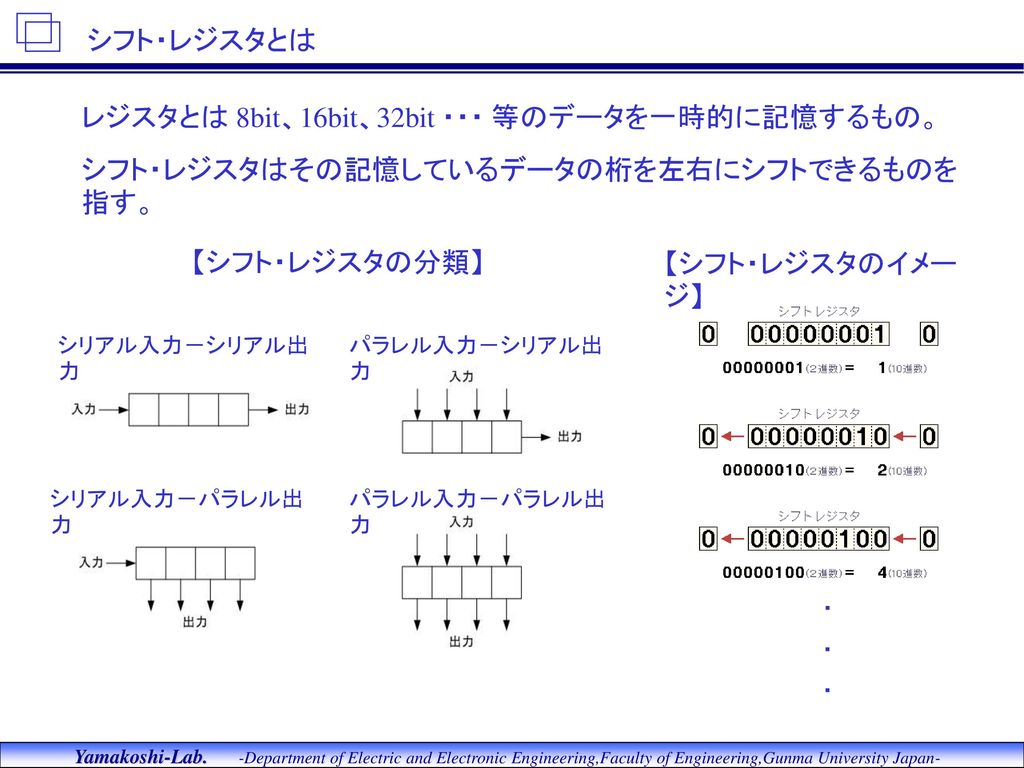

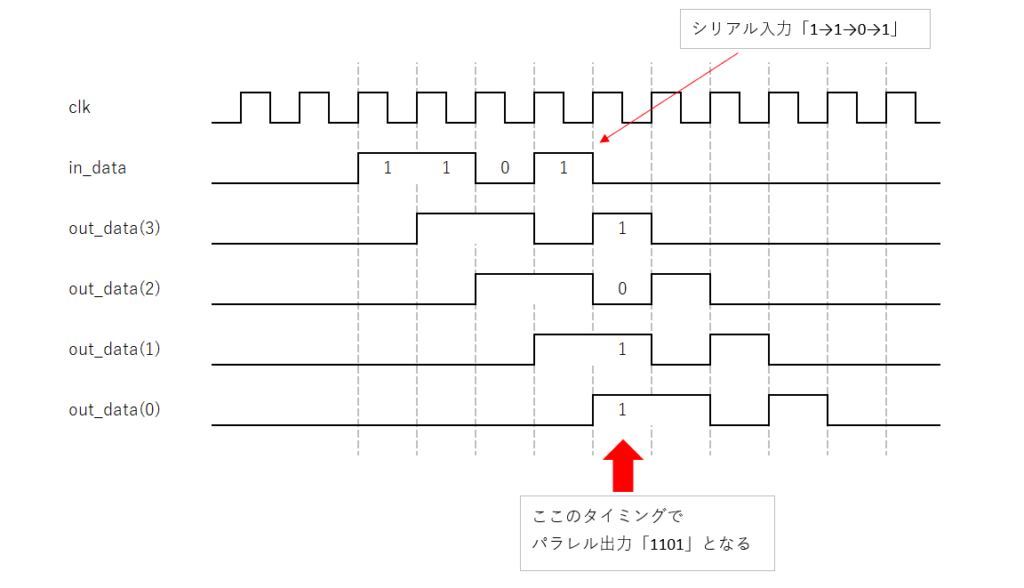

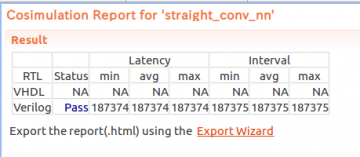

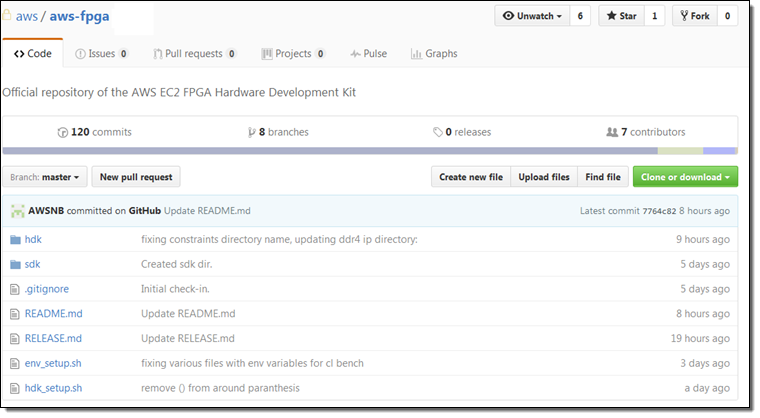

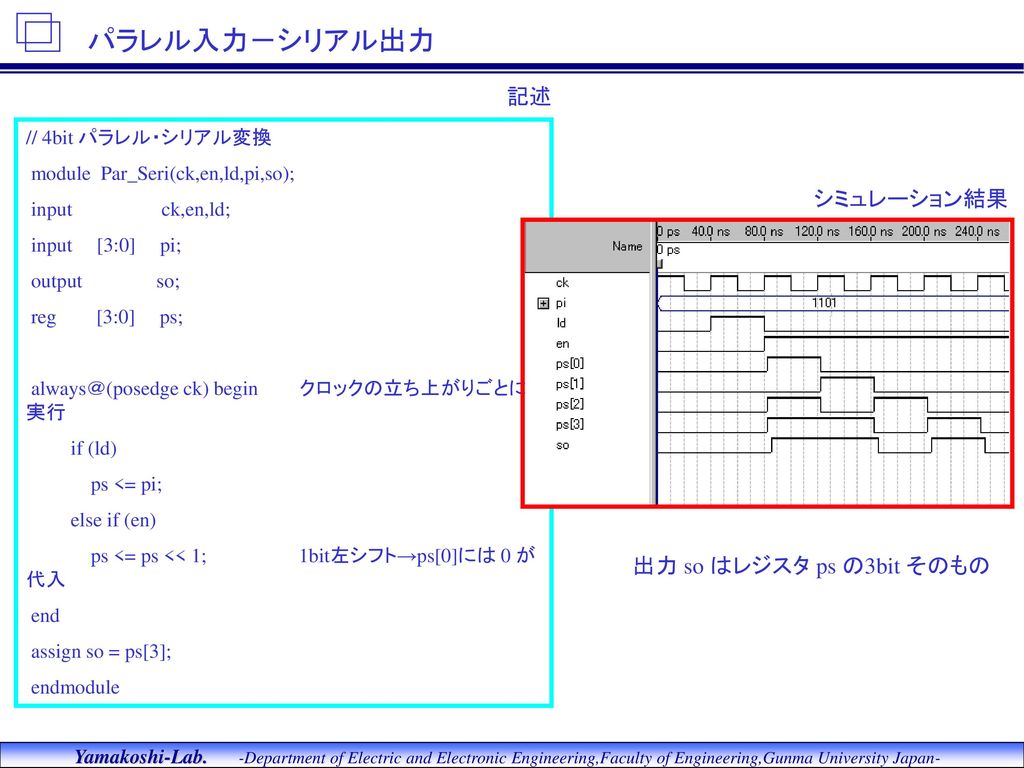

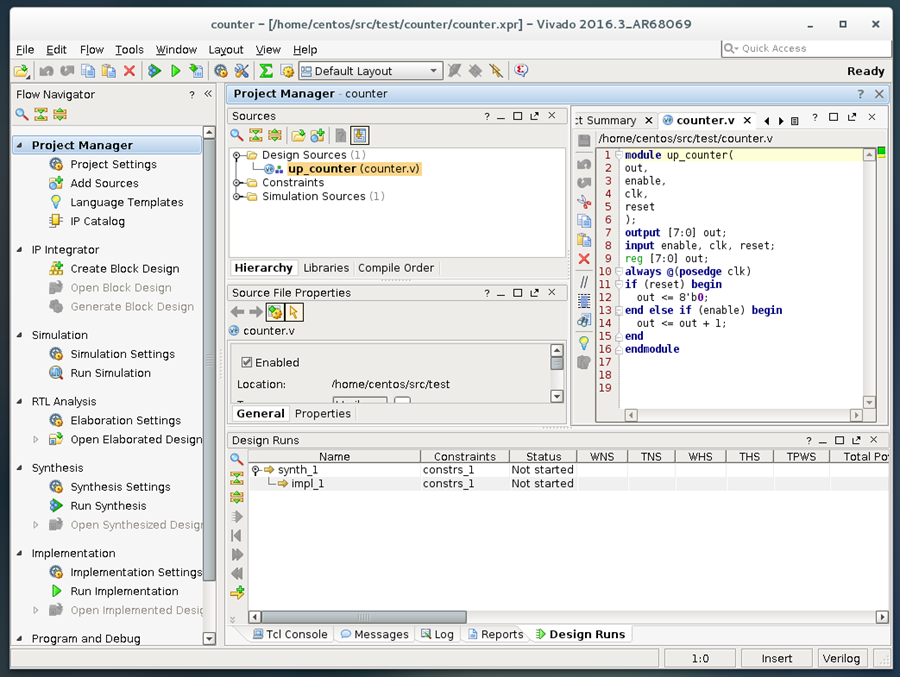

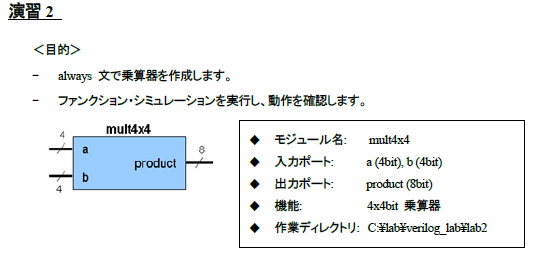

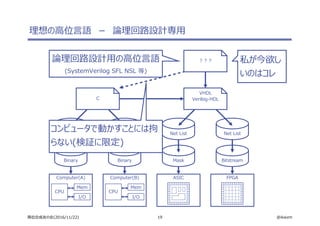

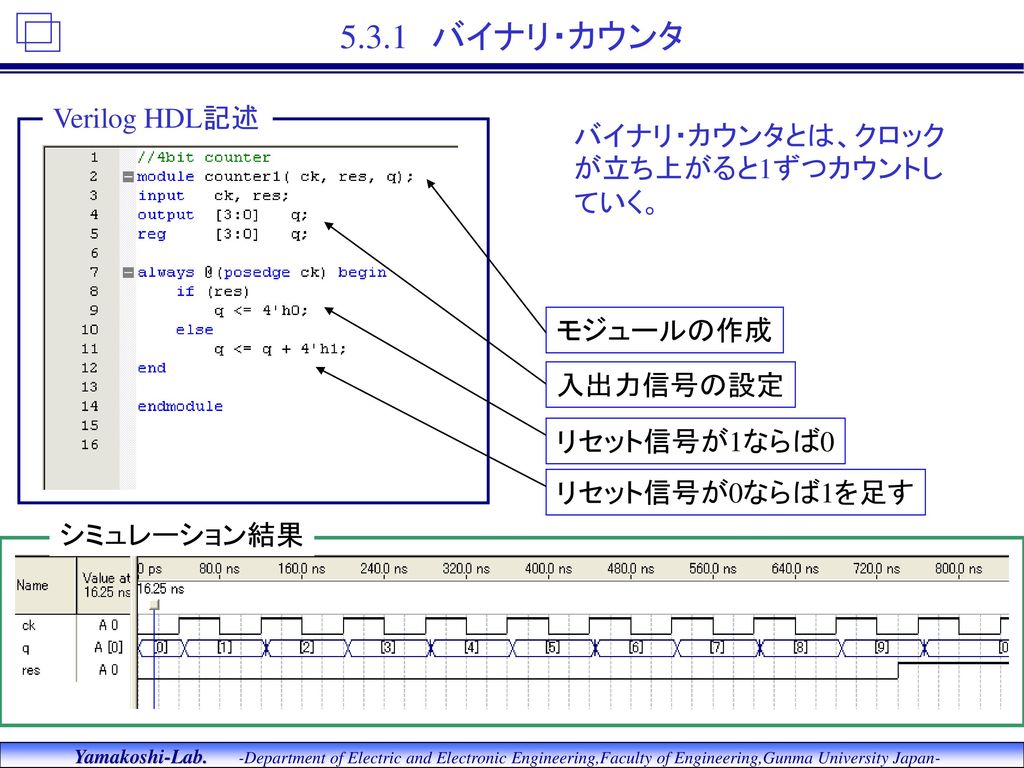

Verilog シフトレジスタ 配列- シフトレジスタの回路図と記述法 (verilog, VHDL) まずシフトレジスタとは、FF (フリップフロップ)を複数用いて値を右から左へ、または左から右へシフトさせるものです。 よく使われる場面として、直列並列変換 (シリアルパラレル変換)があるかなと思いますシフト レジスタの抽出 現在のところ、シフト レジスタ抽出は HDL 属性を使用して行われます。shreg_extract 構文およびその使用方法に関して、131 で UG901 がアップデートされる予定です。 XST で触れられているように次の VHDL/Verilog 構文例は Vivado 合成でサポートされます。

Verilog シフトレジスタ 配列のギャラリー

各画像をクリックすると、ダウンロードまたは拡大表示できます

|  | |

| ||

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

|  | |

|  |  |

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

| ||

| ||

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

| ||

|  |  |

| ||

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  |  |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

| ||

|  |  |

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

|  |  |

|  |  |

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

|  | |

|  | |

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

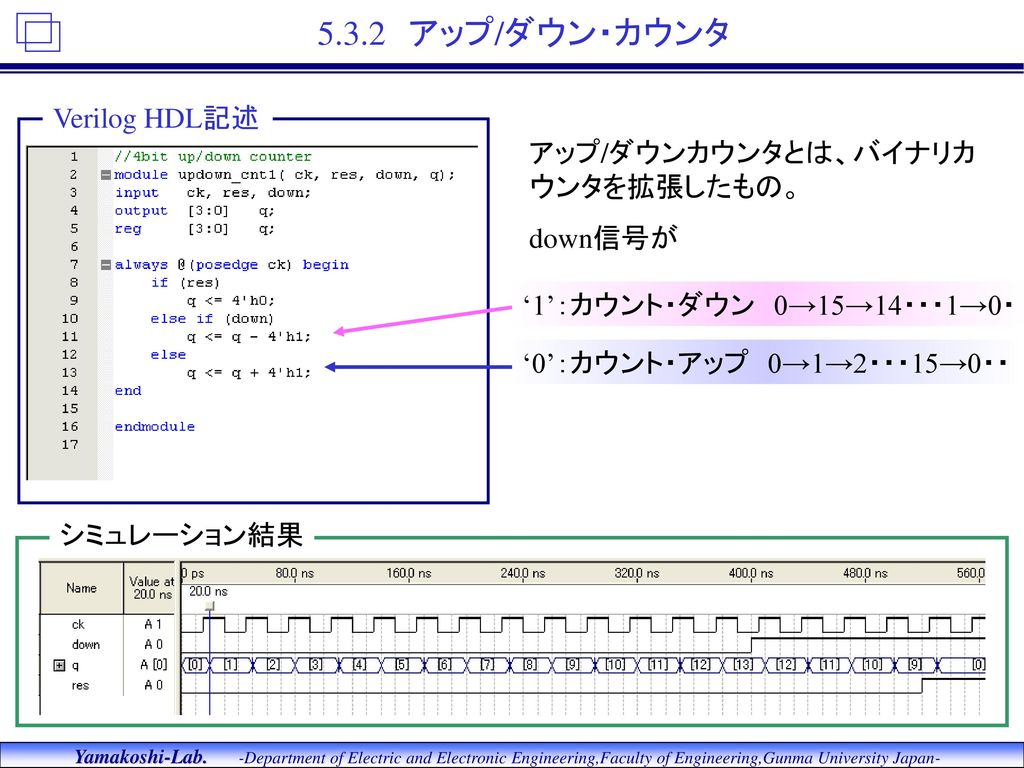

Verilog HDLのカテゴリ演算子は、算術、論理、リレーショナル、ビット単位、シフト、連結、および等式です。 Verilog HDLでは、整数、レジスタ(reg)、ベクトル(regまたはnetデータ型、いくつかのビット長)、および時間の配列が可能です。 配列の基本的なReg レジスタ宣言: 値を保持する変数に対して宣言する。 wire ワイヤ宣言: 配線として使用する変数に対して宣言する。 (assign 文によって常時右辺の結果を出力する) なれないうちは使い分けが難しいので ・always 内で左辺として利用する場合はreg 宣言。

Incoming Term: verilog シフトレジスタ, verilog シフトレジスタ 配列, verilog 多ビット シフトレジスタ, verilog generate シフトレジスタ,

0 件のコメント:

コメントを投稿